**Application note**

#### Document information

| Info     | Content                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | OL2381, BER                                                                                                                                                |

| Abstract | This document describes the OL2381 reference design board, explains the operation of the transmitter and receiver, and provides some application examples. |

| Re | evis | ion | history |  |

|----|------|-----|---------|--|

|    |      |     |         |  |

| Rev | Date     | Description |

|-----|----------|-------------|

| 1   | 20110822 | first issue |

# **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

All information provided in this document is subject to legal disclaimers.

AN11039

2 of 143

# 1. Introduction

This document describes typical applications for the OL2381. It shows a schematic and layout for an application board, describes procedures for setting up the transmitter with FSK and ASK modulation, explains in detail the analog and digital receiver blocks, and describes the procedure for measuring BER. Application examples are provided in <u>Section 8 on page 120</u>.

# 2. Reference design

# 2.1 Schematic

The application board must be carefully designed to achieve high receiver sensitivity and correct transmitter operation.

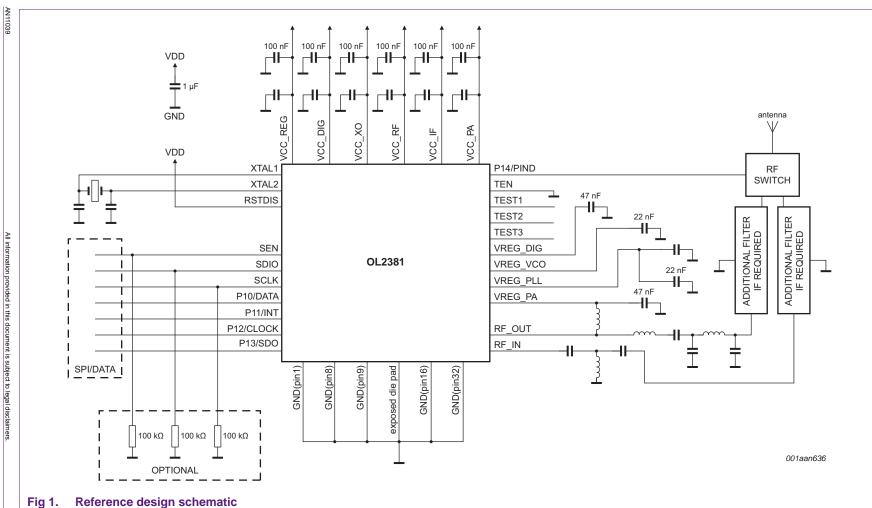

The power supply for the OL2381 requires careful consideration: The OL2381 accommodates four voltage regulators and a dedicated supply connection pin for each of the main functional blocks. All of these connections should be equipped with bypass capacitors to enable noise rejection. The voltage supply should have separate paths to minimize inductive and resistive coupling. All internal blocks are grounded via the exposed die pad on the bottom side of the package. A typical transceiver application using the OL2381 and external components is shown in Figure 1.

3 of 143

The purpose of components used in this schematic is described in <u>Table 1</u>. All parts marked with a star \* are UHF relevant materials and should be chosen according for this purpose. Special attention should be given to self-resonant frequency (SRF) and quality factor Q.

- 22 August 2011

Rev. 1

Application note

#### Table 1. Component description

| · · · · ·                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Component                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| R1, R2, R3                                                  | Pull resistors are required to avoid floating voltage levels at the input ports SEN, SCLK and SDIO since a floating port contributes to increased current consumption. External resistors should be used if the connected SPI controller does not feature internal pull resistors. To disable the OL2381 properly, SEN should be pulled LOW. SCLK and SDIO could be either pulled HIGH or pulled LOW. The value of the external pull resistor should be less than or equal to 1 M $\Omega$ .                                     |

| X1, C2, C3                                                  | External reference crystal resonator components. The values of C2 and C3 should be chosen to support the crystal load capacitance. The values of both capacitors should be identical. If required, the value of C2 can be slightly less than the value of C3.                                                                                                                                                                                                                                                                    |

| C1                                                          | The backup capacitor is specially required for battery supplied applications to avoid power failure during start-up at low temperature.                                                                                                                                                                                                                                                                                                                                                                                          |

| C4 to C15, L1                                               | Noise decoupling capacitors for each OL2381 supply voltage connection<br>pin. Each pin should be equipped with a 100 nF capacitor and a 100 pF<br>capacitor* for high frequency rejection. The low value capacitor should be<br>placed as close as possible to the corresponding supply voltage pin. L1 is<br>optional and could be inserted in order to minimize feedback from the RF<br>power amplifier to other OL2381 functional blocks; at the time of writing, the<br>possibility of eliminating L1 is being investigated. |

| C16 to C19                                                  | A decoupling capacitor is required for each of the internal voltage regulator stages. The value of the capacitor should be chosen as shown in the schematic.                                                                                                                                                                                                                                                                                                                                                                     |

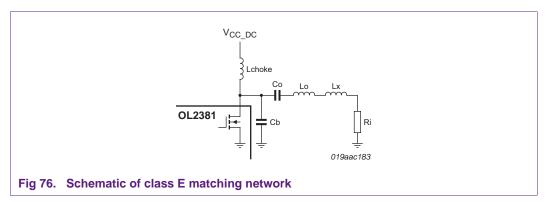

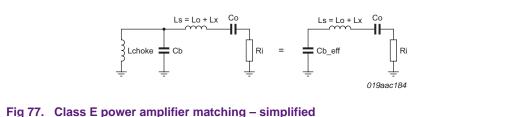

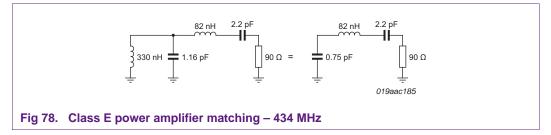

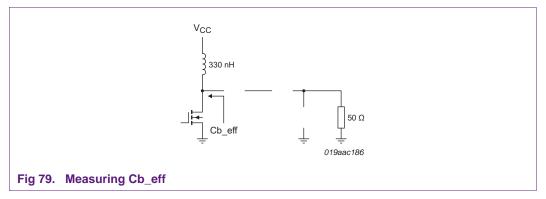

| L2 <sup>[1]</sup>                                           | The choke inductance L2 supplies power to the RF power amplifier. In addition L2 and C27 decouple UHF from the power supply.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                             | L2 is part of the Class E matching network for the power amplifier and reduces the effective capacitance ( $Cb_{eff}$ ) at pin RF_OUT. The value of L2 should be chosen to set the matching according to output power requirements. 315 MHz applications with high output power may require the capacitance to be increased by connecting an additional capacitor directly to pin RF_OUT to GND.                                                                                                                                 |

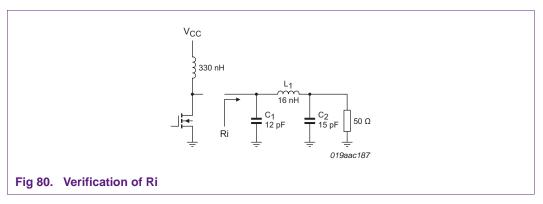

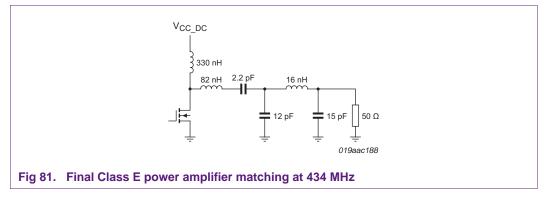

| L3[1], C30[1]                                               | Series resonant circuit of the Class E matching network. The quality of the circuit influences harmonic suppression.                                                                                                                                                                                                                                                                                                                                                                                                             |

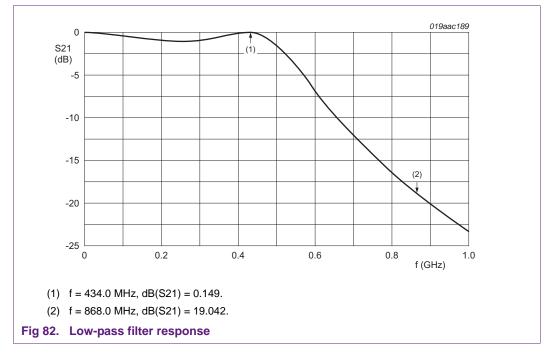

| L4 <sup>[1]</sup> , C31 <sup>[1]</sup> , C32 <sup>[1]</sup> | These elements form a LC low-pass Pi network. The network transforms the antenna impedance to a value required by the class E matching. The quality of the circuit influences harmonic suppression.                                                                                                                                                                                                                                                                                                                              |

| TX additional filter                                        | An additional filter may be required by the application to further increase harmonic suppression. A SAW filter should not be used in the TX path                                                                                                                                                                                                                                                                                                                                                                                 |

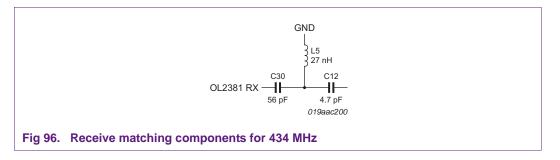

| L5[1], C40[1], C41[1]                                       | These elements form an LC high-pass T network. The network transforms the antenna impedance to the input impedance of RF_IN. A T network is used to minimize signal loss.                                                                                                                                                                                                                                                                                                                                                        |

| RX additional filter                                        | An additional filter may be required by the application to increase interfering signal rejection. A SAW filter can be used for this purpose.                                                                                                                                                                                                                                                                                                                                                                                     |

| RF_IN, RF_OUT                                               | If one of the functions is not used in an application the corresponding pin can remain open.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Component                      | Description                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF switch <sup>[1]</sup> , P14 | The switch combines the RX and TX signal path to a single antenna.<br>OL2381 provides a control signal on P14 to set the state of the switch<br>accordingly.                                                                                                                                                                                        |

|                                | The switch can either comprise discrete components using pin diodes, or an RF switch IC.                                                                                                                                                                                                                                                            |

|                                | If P14 is not used in the application it should remain open.                                                                                                                                                                                                                                                                                        |

| RSTDIS                         | Pin RSTDIS should be connected to either GND or VCC. The initial<br>condition of the polling timer is controlled by this pin.                                                                                                                                                                                                                       |

| SDO                            | SDIO is the configurable bidirectional data input/output pin of the serial interface. By default, the bidirectional mode is configured, so SDIO is used for both input and output data transmission. If SEP_SDO in register PORTCON2 (address: 0x12) is set, SDIO is used as input only and SDO is configured for data output in SPI communication. |

| TEST1, TEST2                   | Pins to output analog test signals of the receiver unit in analog test mode.<br>These pins can be used to debug the analog part of the receiver and so they<br>are connected to test pads. Both pins can remain open.                                                                                                                               |

| TEN, TEST3                     | TEN must be grounded in the application. TEST3 must remain open.                                                                                                                                                                                                                                                                                    |

| P10, P11, P12                  | These ports enable communication between OL2381 and the microcontroller to be separate, allowing different lines for SPI communication and data communication in TX or RX mode.                                                                                                                                                                     |

|                                | After reset the ports are configured for digital output. It is not required to provide pull measurements for these ports.                                                                                                                                                                                                                           |

|                                | These ports provide access to the receiver digital debug interface which requires the ports to be connected to test pads.                                                                                                                                                                                                                           |

Table 1.

Component description ...continued

[1] These are UHF relevant materials and should be chosen for this purpose. Special attention should be given to Self-Resonant Frequency (SRF) and quality factor Q.

### 2.2 Layout

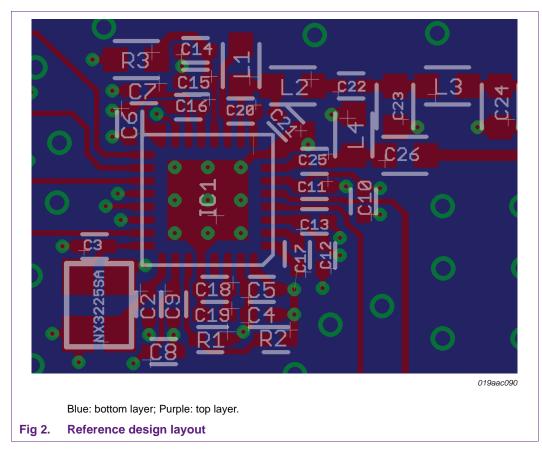

An example of a PCB four layers layout is shown in <u>Figure 2</u>. Additional filters in the RX/TX paths, RF switch and antenna are not shown.

General application note for OL2381

Guidelines for designing the layout are given in Table 2.

AN11039 Application note

| Component                    | Comment                                                                                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground plane on bottom layer | To achieve UHF power transportation with reduced effects due<br>to human hand proximity, a ground plane below the UHF active<br>module and the crystal resonator is recommended.                                                                                                                                  |

|                              | OL2381 functional blocks are connected to ground by the exposed die pad. It is important to have a good connection from the ground plane to the exposed die pad. Nine vias are used below OL2381 for this purpose.                                                                                                |

| Ground plane on top layer    | To reduce noise coupling via ground, several smaller ground<br>fields are placed on the top layer. Special consideration should<br>be given to the routing of the supply voltage bypass capacitors<br>ground connection.                                                                                          |

|                              | Ground planes on both layers should be connected by vias if possible.                                                                                                                                                                                                                                             |

| Class E matching network     | The class E matching components should be placed close to OL2381 above the same ground plane. To setup the matching network properly, especially for high frequency bands, the connection between L2 and L3 as well as the distance to RF_OUT needs to be short to reduce capacitance to ground.                  |

|                              | Long connections or vias between the components can cause<br>additional inductance. This prevents effective filtering and<br>increases unwanted inductive coupling. As a rule of thumb,<br>each cm of PCB wire adds about 10 nH of inductance. This is<br>true also for the ground connection back to the OL2381. |

|                              | L2 and L3 should be placed perpendicular to each other in order to avoid magnetic coupling in-between the coils.                                                                                                                                                                                                  |

|                              | L3 and C30 should be placed close to each other without close ground planes on the top layer, to minimize parasitic capacitance to ground.                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                   |

#### Table 2. Layout guidelines

| Component          | Comment                                                                                                                                                                                                                                                                                             |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Passive components | Most of the components are size 0402 to keep the required PCE space small. In particular, the bypass capacitors at the supply voltage input of OL2381 should be small to place the components close to the IC.                                                                                      |  |  |  |

|                    | The coils in the TX path (L2, L3, and L4) are wound type size 0603. These coils show a good quality factor in order to reduce power loss for the transmitted signal.                                                                                                                                |  |  |  |

|                    | In particular, for the low frequency bands L2 should be a high C coil with a high SFR value. High output power at 315 MHz requires L2 to have a high value in order to get enough capacitance at RF_OUT. Some applications may require an extra capacitor to be connected between RF_OUT and ground |  |  |  |

|                    | The capacitors in the TX and RX paths including the low value bypass capacitors at the voltage ports should be NP0 type. The components in the RF paths and capacitors C1/C2 should have tight tolerance.                                                                                           |  |  |  |

| C3                 | The backup capacitor has a value of 1 $\mu$ F. The component should show low leakage current over the whole temperature range of the application. The device shown in the layout is an X7R type, size 0805.                                                                                         |  |  |  |

| Crystal resonator  | The crystal and corresponding capacitors should be placed<br>close to XTAL1 and XTAL2 to minimize parasitic PCB<br>capacitance and so decrease unwanted detuning due to humar<br>hand proximity in hand-held applications.                                                                          |  |  |  |

#### Table 2.Layout guidelines

EMC measurements are given in <u>Section 9 on page 126</u> with the reference design presented above.

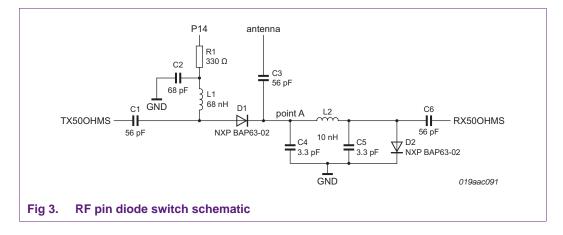

#### 2.3 RF switch

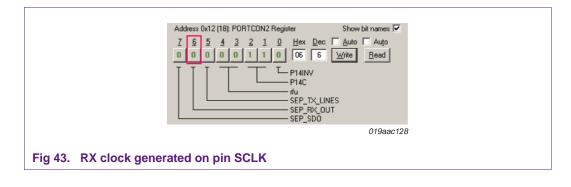

The easiest implementation of the RF switch (transmit/receive) is the single control IC, such as the California Eastern Lab UPD5713. The switch should be controlled by the OL2381 pin P14/IND. When pin P14/IND is LOW, receive mode is activated, and when it is HIGH, transmit mode is activated. OL2381 register PORTCON2 operation bits [2:1] (P14C) should be set to 11 for correct operation; see Figure 43 on page 39.

Dual control ICs can be used. In this case, the switch should be controlled by OL2381 pins P13 and P14.

IC switches available on the market are specified from -45 °C to +85 °C. If the application requires an extended temperature range, the RF switch should comprise discrete components using PIN diodes.

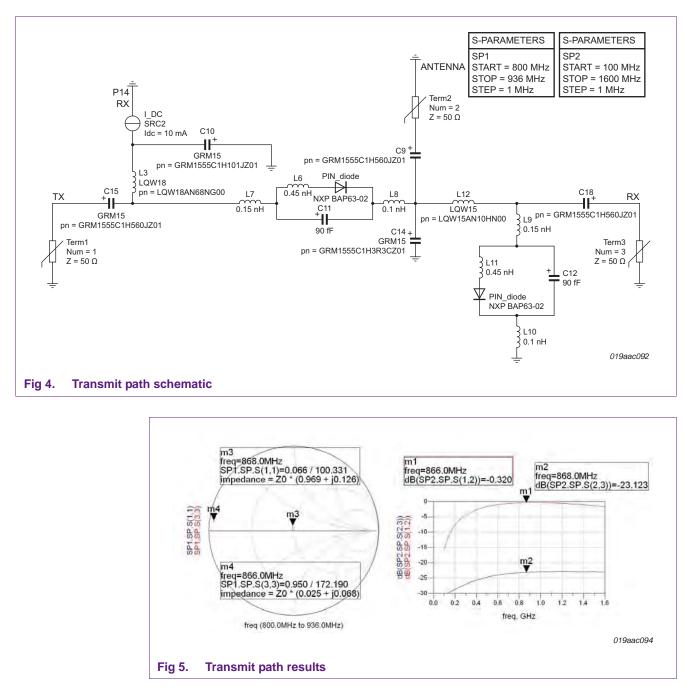

Figure 3 shows the typical quarter wavelength switch and associated grouped elements required for 868 MHz operation. The quarter wavelength circuit (formed by C4, C5, and L2) mainly serves to isolate the transmit path from the receiver input. The PIN diode switch also uses the drive capability of OL2381 pin P14/PIND. When both diodes are forward biased (P14/PIND is HIGH), the transmitter is connected to the antenna and the receiver is protected by the low resistance of D2 terminating the quarter-wavelength line which makes an open-circuit at point A. This allows the signal from TX500HMS to flow through D1 to the antenna. When both diodes are reverse biased (P14/PIND is LOW) the transmitted port is isolated by the high resistance of D1 and the antenna is connected to

RX50OHMS. The high impedance of D2 is transformed to a short-circuit at point A through the quarter wavelength line. Figure 4 and Figure 5 show simulation setup and results for the transmit path. TX50OHMS and RX50OHMS are already matched OL2381 receiver and transmitter ports to 50 W. DC blocking is required by either PIN diode or IC switch, so if series capacitors are used in the receiver, transmitter, and antenna matching networks, then capacitors C1, C6, and C3 can be omitted.

The quarter wavelength transformer has a relatively narrow band response. Instead of C4, C5, and L2, the quarter wavelength line (microstrip line on the PCB) can be used. The quarter wavelength line constrains the bandwidth from 5 % to 10 %. Therefore, for different frequency bands, a different PCB is required.

Advantages of the IC switch compared to the PIN diode switch are: broadband, low insertion loss, good isolation, and small size. Advantages of the PIN diode switch compared to the IC switch are: cost, good linearity, high power applications, and temperature range.

Resistor R1 can be calculated from P14/PIND voltage in the application and diode parameters (forward voltage and current):  $R1 = (VCC - 2 \times VF) / ID$ .

10 of 143

## **NXP Semiconductors**

# AN11039

#### General application note for OL2381

Results are similar for the receive path and are available on request.

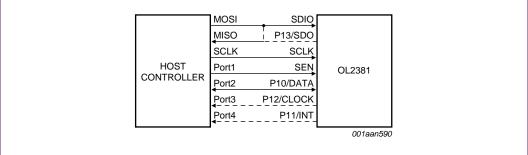

# 3. Interface description

There are two possibilities to send or receive data with the OL2381: by using the SPI pins or by using the general port pins. Registers PORTCON0, PORTCON1 and PORTCON2 (address: 0x10 to 0x12) need to be properly configured. PORTCON0 configures P10/DATA and P11/INT, PORTCON1 configures P12/CLOCK and P13/SDO and

AN11039 Application note PORTCON2 configures P14/PIND and the TX/RX lines. Reset values are: PORTCON0 0x28, PORTCON1 0x0E, and PORTCON2 0x00. Further details are explained in the OL2381 data sheet.

The OL2381 supports three communication modes as shown in Figure 6:

- Minimum of three SPI wires: SEN, SCLK and SDIO

- Full four SPI wires: SEN, SCLK, SDIO line as input and P13/SDO as output

- Separate SPI wires, TX/RX data and clock lines: P10 as TX/RX data and P12 for clock

|            | MOSI      | SDIO      |           |   |

|------------|-----------|-----------|-----------|---|

|            | MISO<br>◀ | P13/SDO   |           |   |

|            | SCLK      | SCLK      |           |   |

| HOST       | Port1     | SEN       | OL2381    |   |

| CONTROLLER | Port2     | P10/DATA  |           |   |

|            | Port3     | P12/CLOCK |           |   |

|            | Port4     | P11/INT   |           |   |

|            | 1.        | L         | 001aan590 | ) |

### 3.1 SPI communication

Pull measurements are required to avoid floating voltage levels at the input of SEN, SCLK and SDIO. Details are given in <u>Table 1 on page 5</u>.

The SPI protocol is always used to configure the OL2381 registers. The data rate should not be higher than 4 MHz.

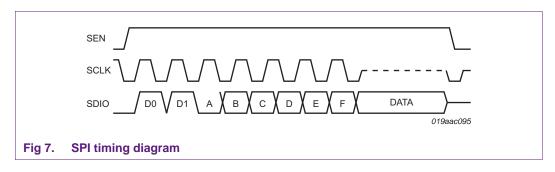

There are four SPI commands: READ, WRITE, TRANSMIT and RECEIVE as described in <u>Table 3 on page 13</u>. A command can only be executed if line SEN is HIGH. Every command must be terminated by pulling SEN LOW. It is possible to interrupt every command by pulling SEN LOW. If SCLK is HIGH at the rising edge of SEN, the data is transferred with the rising edge of SCLK. If SCLK is LOW on the rising edge of SCLK, data is transferred on the falling edge of SCLK as shown in <u>Figure 7</u>.

| Table 3. | SPI commands |           |                        |

|----------|--------------|-----------|------------------------|

| D0       | D1           | Command   | A to F                 |

| 0        | 0            | write SFR | start address A5 to A0 |

| 0        | 1            | read SFR  | start address A5 to A0 |

| 1        | 0            | receive   | receive options        |

| 1        | 1            | transmit  | transmit options       |

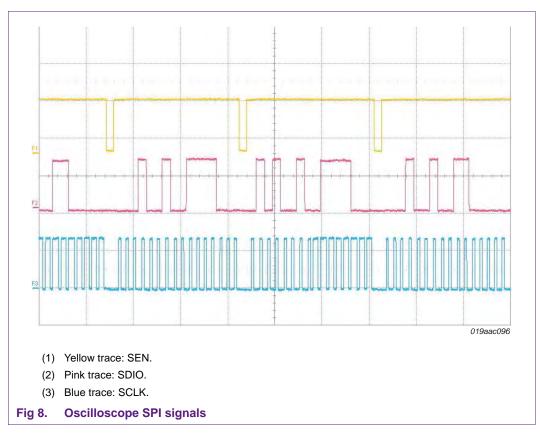

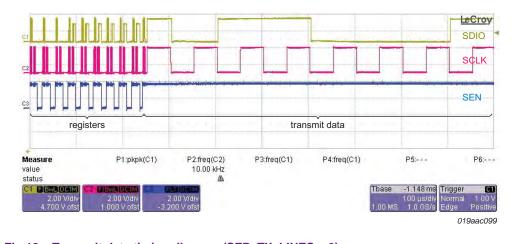

Figure 8 shows an oscilloscope view of the SPI communication. The yellow trace represents the SEN line, the pink trace the SDIO line and the blue trace the SCLK line.

After line SEN goes down and up, data is transferred to OL2381 according to Figure 7. This can be seen in Figure 8. The first SPI command is write command (00b) to the address of 0x11 (010010b) which corresponds to register PORTCON1. The value 0x78 (0111 1000b) is then written to this register.

The second SPI command is read command (01b) from address 0x11 (010010b) which corresponds to register PORTCON1. The value 0x78 (0111 1000b) is then read from this register.

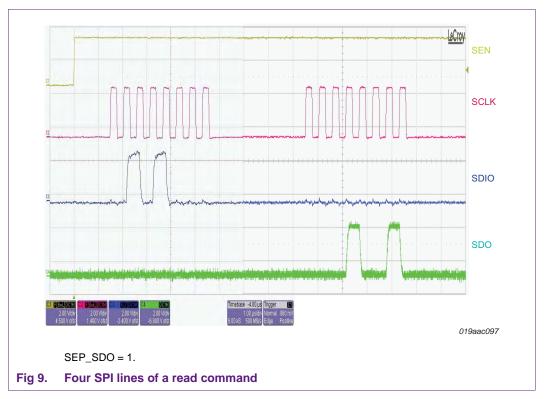

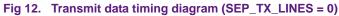

<u>Figure 9</u> shows a read command with four lines: SEN, SCLK, SDI and SDO (SPI interface). In this case, bit SEP\_SDO in register PORTCON2 must be set to logic 1.

General application note for OL2381

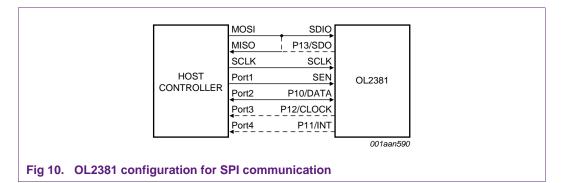

When a SPI data communication is used as shown in <u>Figure 10</u>, the SPI pins are used to configure the OL2381 registers and to exchange data.

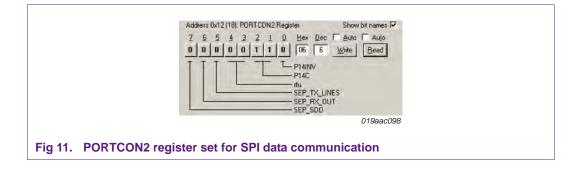

Bits SEP\_TX\_LINES and SEP\_RX\_OUT in register PORTCON2 should be set to logic 00 for a SPI data communication. This is shown in Figure 11.

General application note for OL2381

Figure 12 and Figure 13 show transmit and receive data timing diagrams when SPI data communication is used.

## 3.2 Port communication

Figure 14 shows the block diagram of the port in-use communication. The SPI pins are used to configure the OL2381 registers. Ports P10, P11, and P12 are used to send or receive data, clock and interrupt.

Fig 14. OL2381 Configuration for port communication

Pin P10/DATA is used for TX/RX data input/output, P12/CLOCK delivers the associated clock signal and P11/INT can be configured for data or interrupt output between the OL2381 and host controller.

These three output pins deliver the result of the receiver when it is configured for normal mode. DATA is the data output, CLOCK delivers the associated clock signal and INT is usually used as an interrupt request.

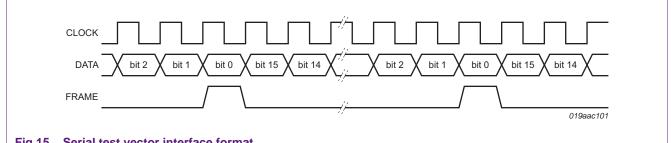

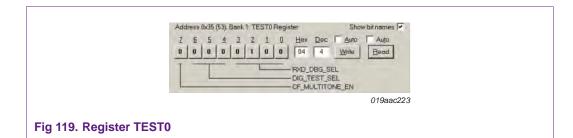

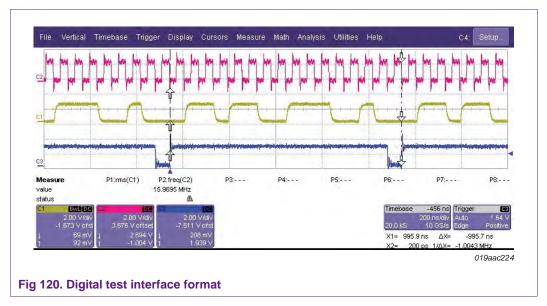

By setting the register field RXD DBG SEL in register TEST0 (address: 0x35) to a non-zero value, the receiver is configured for digital debug mode. In this mode, normal function of ports (P10, P11, and P12) is overwritten with the fast 3-wire synchronous serial interface function. In this mode P12 outputs 16 MHz serial clock, P10 outputs the serial data, and P11 outputs a synchronization pulse for each serial 16-bit data word.

The protocol used in this mode is shown in Figure 15. In this case, the OL2381's current consumption will increase by 5 mA.

Fig 15. Serial test vector interface format

Bits SEP\_TX\_LINES and SEP\_RX\_OUT in register PORTCON2 (see Figure 11 on page 14) should be set to logic 11 for normal port data communication.

Table 4 gives the port configuration summary.

# **NXP Semiconductors**

#### General application note for OL2381

| Table 4. Port  | configuration             |                                                                     |                                           |                           |                               |                                                                            |

|----------------|---------------------------|---------------------------------------------------------------------|-------------------------------------------|---------------------------|-------------------------------|----------------------------------------------------------------------------|

| Description    | PORTCON0                  |                                                                     | PORTCON1                                  |                           | PORTCON2                      |                                                                            |

| Value:         | 0x28                      |                                                                     | 0x04                                      |                           | 0x66                          |                                                                            |

| Ports:         | P10/DATA                  | P11/INT                                                             | P12/CLOCK                                 | P13/SDO                   | P14                           | SEP_RX_OUT,<br>SEP_TX_LINES                                                |

| Configuration: | P10 is in 3-state<br>mode | P11 = 0010b +<br>P11 INV; P11<br>behaves as<br>interrupt<br>request | P12 provides<br>the RX/TX<br>clock output | P13 is in 3-state<br>mode | P14 controls<br>the RF switch | P10 is always<br>used as RX/TX<br>data and P12 as<br>RX/TX clock<br>output |

#### Table 4.Port configuration

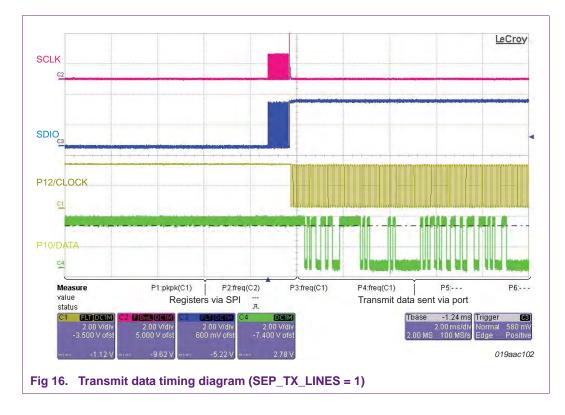

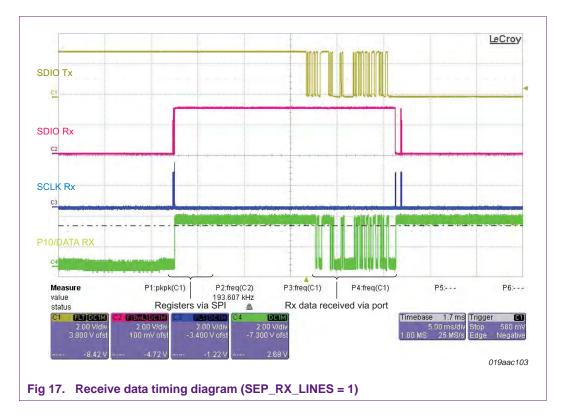

Figure 16 and Figure 17 show transmit and receive data timing diagrams when port communication is used.

General application note for OL2381

# 4. Phase-locked loop

The complete on-chip Phase Locked Loop (PLL) provides an RF carrier both in the Transmit (TX) and Receive (RX) mode. The PLL is a 4th-order fractional-N PLL. It is designed for a current output phase detector. It comprises a 2nd-order integrating filter, followed by an additional pole to reduce the phase reference spur modulation of the VCO. The PLL main divider consists of one fixed (divided by 2) and five switched dividers (5 control bits for 32 different divider settings) with a range of 64 to126. More details are given in the OL2381 data sheet.

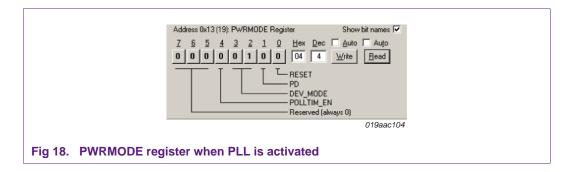

All PLL blocks except VCO\_BAND and the charge pump current (ICP\_PLL settings) are automatically configured and operated by selecting the corresponding device modes. Two bits (DEV\_MODE[3:2]) in register PWRMODE (address: 0x13), control the active modes of the device.

| Table 5. | DEV_MODE[1:0] device mode control functions |                                                                                                                                                                 |  |

|----------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D3       | D2                                          | Function                                                                                                                                                        |  |

| 0        | 0                                           | crystal oscillator or external clock buffer is enabled and after crystal oscillator stabilization (if selected) the device is supplied with the reference clock |  |

| 0        | 1                                           | PLL controlled local oscillator (LO) enabled. LO power-up<br>procedure includes VCO sub-band calibration<br>(unconditionally) and PLL lock-in detection         |  |

| 1        | 0                                           | prepare and enable RX operation. LO enabled and after PLL acquires lock, RX is switched on and enabled                                                          |  |

| 1        | 1                                           | prepare and enable TX operation. LO enabled and after PLL acquires lock, TX path and PA regulator are switched on and enabled.                                  |  |

Three important static enable signals are decoded from the DEV\_MODE, namely PLLEN, TXEN and RXEN. PLLEN is set whenever the DEV\_MODE is not logic 00. These three signals are internal and not accessible to customers.

## 4.1 PLL operation

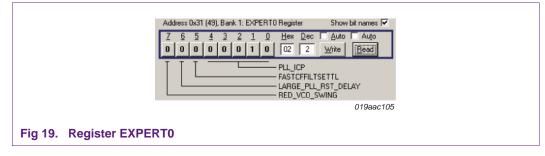

The charge pump delivers charge to the loop filter. The polarity and amount of charge are proportional to the phase error reported by the phase detector (PFD). The five PLL ICP control bits in register EXPERT0 (address: 0x31) shown in Figure 19, are reserved for manual programming of PLL charge pump current. The value from 15  $\mu$ A to 465  $\mu$ A can be selected with the formula:  $I_{cp} = PLL\_ICP \times 15 \ \mu A$ .

The recommended value is ICP2.

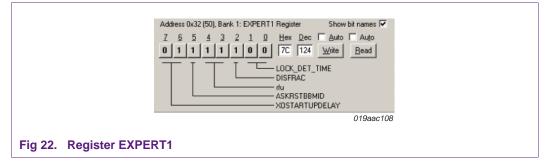

The lock detection circuit monitors the phase and frequency difference of PLL in order to detect the shortest PLL power-on time. The lock detection circuit can be manually controlled by bit LOCK\_DET\_ON in register LOCON (address: 0x0D). After the time defined by bits LOCK\_DET\_TIME in register EXPERT1 (Figure 22 on page 23), status bit LO\_RDY is set in register DEVSTATUS (address: 0x19).

# 4.2 Operating frequency

The PLL operating frequency is set by registers FC0x (address: 0x00 to 0x01 to 0x02), FC1x (address: 0x03 to 0x05), FC2x (address: 0x06 to 0x08), and FC3x (address: 0x09 to 0x0B). Each of them (0, 1, 2, or 3) has a width of 20 bits and can be selected directly with bits A and B in transmit or receive command.

The selection and description of the frequency control registers are given in Table 6.

| Table 0. Trequency selection register bit settings |              |                              |  |  |

|----------------------------------------------------|--------------|------------------------------|--|--|

| A (TX or RX)                                       | B (TX or RX) | Selected frequency registers |  |  |

| 0                                                  | 0            | FC0L, FC0M, FC0H             |  |  |

| 0                                                  | 1            | FC1L, FC1M, FC1H             |  |  |

| 1                                                  | 0            | FC2L, FC2M, FC2H             |  |  |

| 1                                                  | 1            | FC3L, FC3M, FC3H             |  |  |

|                                                    |              |                              |  |  |

Table 6. Frequency selection register bit settings

The frequency control registers (FCxL, FCxM and FCxH) contain the integer and fractional part of the operating frequency described in <u>Table 7</u>.

| Table 7. | Frequency setting registers |

|----------|-----------------------------|

|          |                             |

| Register | Bit                                                                 |   |   |          |                   |          |   |         |

|----------|---------------------------------------------------------------------|---|---|----------|-------------------|----------|---|---------|

|          | 7 (MSB)                                                             | 6 | 5 | 4        | 3                 | 2        | 1 | 0 (LSB) |

| FCxL     | Lower 4 bits of fractional part of operating frequency FCx not used |   |   |          |                   |          |   |         |

| FCxM     | Middle 8 bits of fractional part of operating frequency FCx         |   |   |          |                   |          |   |         |

| FCxH     | 5 integer bits of operating frequency                               |   |   | higher 3 | B bits of fractio | nal part |   |         |

|          |                                                                     |   |   |          |                   |          |   |         |

The 20 binary bits in the PLL frequency registers can be calculated using the formula Equation 1 when bit DOUBLE\_SD\_RESULT = logic 0.

$$FCx = \left\lfloor \left( \frac{f_{RF}}{f_{ref}} \times (1 + RF\_LO\_DIV) - 32 \right) \times 32768 \right\rfloor$$

(1)

Where:  $f_{RF}$  is the frequency to be computed (434 MHz),  $F_{ref}$  is the crystal reference frequency, which for this application is 16 MHz.

It is possible to determine the values of the three registers FCxH, FCxM and FCxL when bit DOUBLE\_SD\_RESULT = logic 1 by using the inverse function of the frequency shown in Equation 2, Equation 3 and Equation 4.

$$f_{RF} = f_{ref} \times \left\{ 32 + FCx[19:15] + \frac{2 \times FCx[14:0] + 1}{32768} \right\} \times \frac{1}{1 + \text{RF}\_\text{LO}\_\text{DIV}}$$

(2)

$$FCx[19:15] = \left\lfloor \frac{f_{RF}}{f_{ref}} \times (1 + \text{RF}_{LO}_{DIV}) - 32.5 \right\rfloor$$

(3)

$$FCx[14:0] = \left[ \begin{cases} f_{RF} \\ f_{ref} \end{cases} \times (1 + \text{RF}_LO_DIV) - 32 - FCx[19:15] \end{cases} \times 16384 \right]$$

(4)

Where:

$f_{\text{RF}}$  is the frequency to be computed, here 434 MHz.

$f_{ref}$  is the crystal reference frequency, which for this application is 16 MHz.

FCx[19:15] corresponds to the integer bits.

FCx[14:0] corresponds to the fractional part bits.

Table 8 presents the configuration registers for some OL2381 operating frequencies.

| Frequency (MHz) | Frequency select |      | RF_LO_DIV |   |  |  |

|-----------------|------------------|------|-----------|---|--|--|

|                 | FCxH             | FCxM | FCxL      |   |  |  |

| 315             | 0x3B             | 0x00 | 0x00      | 1 |  |  |

| 434             | 0xB2             | 0x00 | 0x00      | 1 |  |  |

| 868             | 0xB2             | 0x00 | 0x00      | 0 |  |  |

| 915             | 0xC9             | 0x80 | 0x00      | 0 |  |  |

Table 8.

Frequency selection registers bits setting for different carrier frequencies

Some frequency settings should not be used. More details are given in <u>Section 4.3.3 on</u> page 24.

#### 4.2.1 VCO auto calibration and sub-band selection

The VCO calibration is performed when the VCO is turned on and every time when:

- the frequency changes with a transmit or receive command,

- the MSByte of the currently selected frequency setting changes,

- the VCO band changes with bit VCO\_BAND,

- the sigma-delta mode changes with DOUBLE\_SD\_RESULT,

- switching between TX and RX.

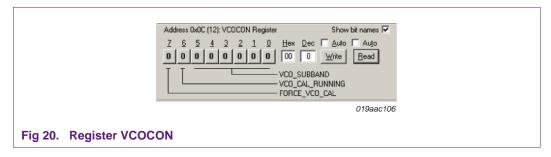

The automatic VCO calibration can be suppressed in the some cases (more details are given in the OL2381 data sheet) by setting bit SKIP\_VCO\_CAL in register LOCON. The resulting sub-band settings from the VCO calibration can be read out via bit VCO\_SUBBAND in register VCOCON. This value can be overwritten at any time by the microcontroller. If the value is written during an ongoing calibration, the result will become undefined. The FORCE\_VCO\_CAL bit in register VCOCON can be used to start a VCO calibration unconditionally on microcontroller request.

The VCO auto-calibration routine automatically trims the VCO to the correct sub-band whenever a different frequency setting is used in TX or RX operation and VCO calibration is carried out automatically. The sub-band selection can be manually modified by control bits VCO\_SUBBAND in register VCOCON as shown in Figure 20.

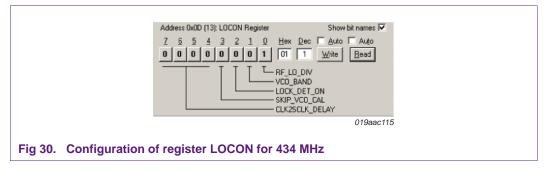

Bit RF\_LO\_DIV in register LOCON (address: 0x0D) defines the division factor for VCO frequency. If RF\_LO\_DIV is logic 0, the VCO frequency is divided by 2 to achieve an operating frequency above 500 MHz. If RF\_LO\_DIV is logic 1, the VCO frequency is divided by 4 to achieve the operating frequency below 500 MHz.

21 of 143

Bit VCO\_BAND in register LOCON must be set to logic 1 for frequency bands below 400 MHz while it is zero for all other bands. In this case the VCO frequency is divided by 2. The VCO is running at twice (868 MHz and 915 MHz) and four times (315 MHz and 434 MHz) the selected frequency band as described in Table 9.

| Table 9. V | /CO | and | carrier | outp | ut freq | uencies |

|------------|-----|-----|---------|------|---------|---------|

|------------|-----|-----|---------|------|---------|---------|

| Device     | Frequ | ency (M | Hz) | RF VCO (MHz)                                      |

|------------|-------|---------|-----|---------------------------------------------------|

|            | Min   | Тур     | Max |                                                   |

| OL2381 VCO | 300   | 315     | 320 | 300 MHz x 4 to 320 MHz x 4 = 1200 MHz to 1280 MHz |

| bands      | 415   | 434     | 450 | 415 MHz x 4 to 928 MHz x 2 = 1660 MHz to 1856 MHz |

|            | 865   | 868     | 870 |                                                   |

|            | 902   | 915     | 928 |                                                   |

## 4.3 PLL measurement results

#### 4.3.1 Phase noise measurements

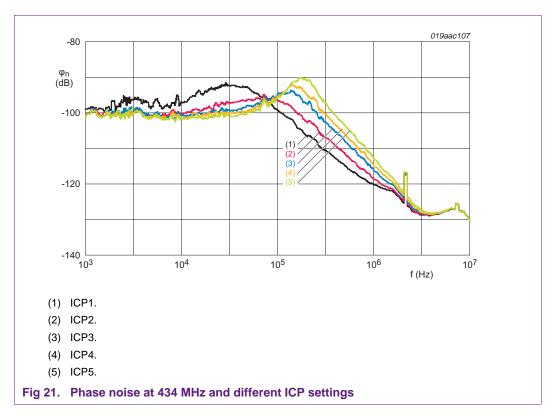

Figure 21 shows the measured phase noise results for 434 MHz. The results for other frequency bands (315 MHz, 868 MHz and 915 MHz) are similar and available upon request.

The PLL loop bandwidth set by PLL\_ICP2 is the best trade-off between noise behaviors and locking time. It is recommended that the PLL loop bandwidth should be set to 150 kHz.

At low frequency bands (315 MHz or 434 MHz), an internal divider is used in the PLL to provide the required frequency. When this divider is on, the phase noise is about 6 dB lower than for the high frequency bands (868 MHz or 915 MHz).

AN11039 Application note

### General application note for OL2381

### 4.3.2 PLL locking time

The lock detection circuit monitors the phase and frequency difference of the PLL and reference clock. The status bit LO\_RDY is set in register DEVSTATUS (address: 0x19) after an additional delay specified by bits LOCK\_DET\_TIME in register EXPERT1 (address: 0x32).

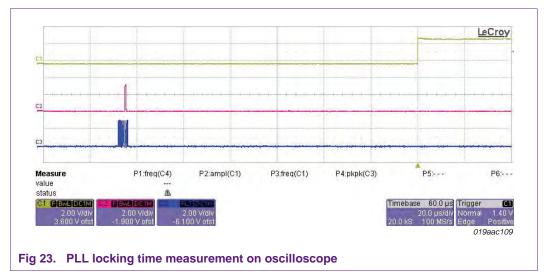

The setup for measuring the PLL locking time is:

- Set register PORTCON0 to 0101xxxx to make the LO\_RDY flag bit appear at output pin P11/INT

- The PLL is set whenever bits DEV\_MODE[3:2] in register PWRMODE are not zero [00]. Switching bits DEV\_MODE from [00] to any other state can be used as a reference start time for PLL locking time measurement

- Set the oscilloscope trigger to LO\_RDY flag (P11/INT).

23 of 143

After switching the DEV\_MODE bits from [00] to any other state, measure the time from last SPI clock (SCLK) to the time when LO\_RDY flag goes HIGH (PLL locked). It should be close to 120 μs.

Figure 23 shows the results for PLL locking time. The measurement is performed with the charge pump current ICP2 setting.

In Figure 23, the yellow trace is the LO\_RDY flag signal at pin P11/INT, the red trace is the write command data on SPI line SDIO, and the blue trace is the SPI clock measured on pin SCLK. PLL locking time is close to 120  $\mu$ s.

### 4.3.3 Frequency range

### 4.3.3.1 Inappropriate FC settings

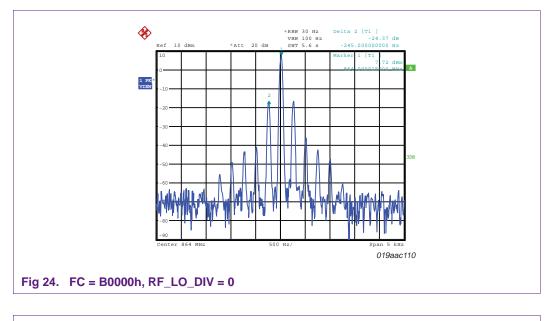

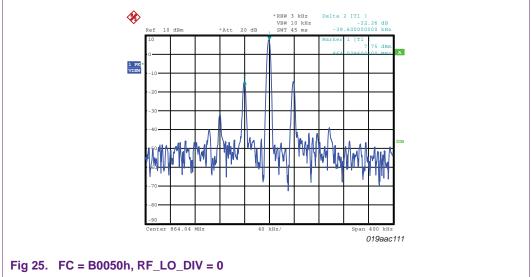

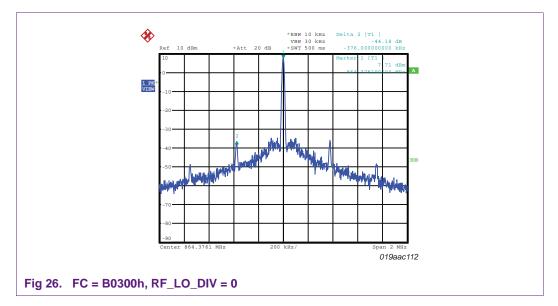

For specific settings of the frequency control value FC, the OL2381 fractional-N PLL creates a frequency modulated output instead of a clean carrier signal. The disturbing signal could be observed in the output signal frequency spectrum appearing as spurious emissions close to the carrier frequency. The modulation frequency and the FM modulation index of the disturbing signal depend directly on the FC settings.

### General application note for OL2381

If the 14 LSBits of FC are interpreted as a signed integer, the modulation frequency of the disturber increases with the absolute value of this number. Due to the filter function of the PLL loop filter, the modulation index depends on the modulation frequency of the disturber. With the recommended setting of ICP = 2 the maximum modulation index is about 1 / 5, in other words the maximum power in the spurious emission is -20 dBc.

In order to minimize the influence of the disturbing signal to the application, especially if OL2381 is in receive mode, and to avoid interference with adjacent channels in transmit mode, some values of FC should be avoided.

RF\_LO\_DIV = 1 (256 MHz to 512 MHz)

a range of  $\pm 1024$  should be avoided around FC = N  $\times$   $2^{16}$  (0  $\leq$  N  $\leq$  16)

a range of ±512 should be avoided around FC = N  $\times$  2^{15} (0  $\leq$  N  $\leq$  32)

a range of ±256 should be avoided around FC = N  $\times$  2<sup>14</sup> (0  $\leq$  N  $\leq$  64)

If the values listed above are avoided, the modulation frequency of the disturber is  $\ge 250$  kHz and the modulation index is  $\le 1 / 50$  (the power in the spurious emissions is < -40 dBc).

RF\_LO\_DIV = 0 (512 MHz to 1024 MHz)

a range of  $\pm$ 768 should be avoided around FC = N × 2<sup>15</sup> (0 ≤ N ≤ 32)

a range of  $\pm 384$  should be avoided around FC = N  $\times 2^{14}$  (0  $\leq$  N  $\leq$  64)

If the values listed above are avoided, the modulation frequency of the disturber is  $\geq$  375 kHz and the modulation index is  $\leq$  1 / 50 (the power in the spurious emissions is < -40 dBc).

The influence of flag Double\_SD\_Result to the spurious emission is small. If the flag is set, the output signal will show an increased phase noise. Avoid configuring the OL2381 to FSK in transmit mode if the flag is set.

#### 4.3.3.2 Extreme FC values

The VCO's frequency range is optimized for the 315 MHz, 434 MHz, 868 MHz, and 915 MHz band. However the accessible frequency range of OL2381 is not limited to these ISM bands. The extreme values of FC have been determined by measuring the RF output.

| Table 10. VC      | le 10. VCO_BAND = 0 |           |                                             |  |  |

|-------------------|---------------------|-----------|---------------------------------------------|--|--|

| FC <sup>[1]</sup> |                     | RF_LO_DIV | f <sub>RF</sub> @ f <sub>REF</sub> = 16 MHz |  |  |

| 60000h            | 393216d             | 1         | 352 MHz                                     |  |  |

| F0000h            | 983040d             | 1         | 496 MHz                                     |  |  |

| 60000h            | 393216d             | 0         | 704 MHz                                     |  |  |

| F0000h            | 983040d             | 0         | 992 MHz                                     |  |  |

[1] FCmin = 60000h (limited by VCO range); FCmax = F0000h (limited by design).

AN11039 Application note

## Table 11. VCO\_BAND = 1

| FC[1]  |         | RF_LO_DIV | f <sub>RF</sub> @ f <sub>REF</sub> = 16 MHz |

|--------|---------|-----------|---------------------------------------------|

| 18000h | 98304d  | 1         | 280 MHz                                     |

| 58000h | 360448d | 1         | 344 MHz                                     |

| 18000h | 98304d  | 0         | 704 560                                     |

| 58000h | 360448d | 0         | 688 MHz                                     |

[1] FCmin = 18000h (limited by VCO range); FCmax = 58000h (limited by VCO range).

#### 4.3.3.3 Frequency range, f<sub>REF</sub> = 16 MHz

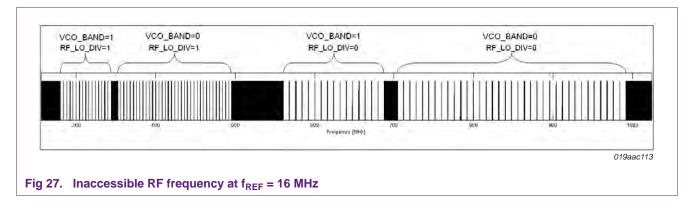

The limitations for FC given above are visualized in <u>Figure 27</u> and calculated for a reference frequency of 16 MHz.

# 5. General register configuration

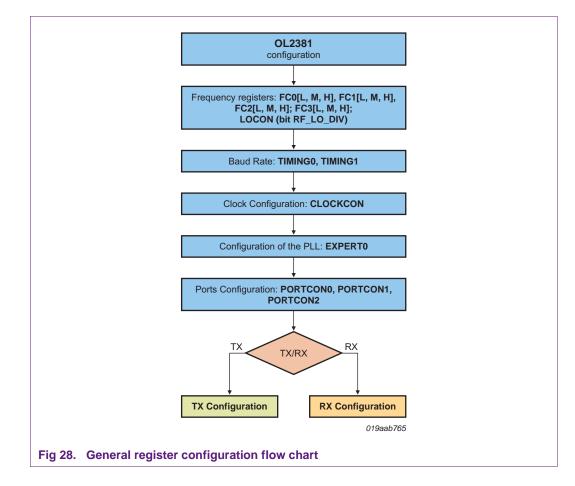

Figure 28 is a flow chart showing the configuration of the OL2381 general registers required to run an application (TX or RX).

#### 5.1 OL2381 reset

It is highly recommended to reset the OL2381 by writing logic 1 to bit RESET in register PWRMODE (see <u>Figure 18 on page 18</u>) before starting to configure the general registers. There should be no current flowing into the circuit. Then, reading the value of register PWRMODE should clear bit RESET to logic 0. Total supply current should be about 1.2 mA.

# 5.2 Brownout detection

Brownout detection is used on all voltage regulators except digital. Reset level is about 1.75 V. Brownout threshold is 1.65 V. This means that the brownout threshold is lower than the reset level. Therefore, if the battery is too weak to supply adequate current and VCC drops below 1.75 V, the OL2381 resets instead of only indicating a brownout. If something happens to the digital regulator (overload), a master reset occurs.

Brownout detectors are in the PLL, VCO and PA regulators, and they can be used in the applications. Regulators can deliver 24 mA (40 mA for the PA). The nominal voltage for each of these regulators is 1.8 V and if the dropout voltage is greater than 100 mV the

brownout flag is set in the IFLAG register. This can notify the microcontroller that something unexpected happened, such as overloaded PLL, VCO and PA regulators, or something unusual in the PA antenna matching path). Reading the IFLAG register and especially brownout flag clears the register and sets the device back to the original mode of operation. For example, if the device was in receive mode and, for some reason, the brownout flag is set, reading the IFLAG register clears the register and returns the device to receive mode.

An unwanted behavior can happen when using the brownout detection. Two cases can induce this behavior:

- If a brownout occurs after a TX command with activation edge but before any other command, then reading the IFLAG re-activates the transmission. Reading the register IEN may also re-activate the transmission but it does not clear flag IF\_BROWNOUT in register IFLAG.

- If the brownout occurs after any other command, then reading the IFLAG will not reactivate the transmission

To ensure that a transmission is not automatically resumed after reading register IFLAG, the application needs to proceed as follows:

If an interrupt occurs after activating the transmitter:

- 1. Read the register DEVSTATUS.

- 2. If bit PA\_PWR\_RDY is not set, then bits DEV\_MODE have to be set to 01b (PLL enable).

- 3. Read the register IFLAG.

### 5.3 Frequency and PLL settings

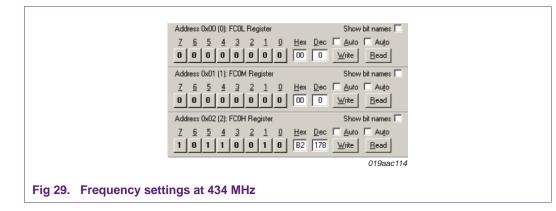

After resetting the OL2381, the operating frequency should be set. Four different frequencies can be stored in registers FC0L to FC3H (address: 0x00 to 0x0B). Frequency selection (one of these four choices) is made by flags in transmit command, receive command, or POLLACTION register. In this document only FC0 is set to 434 MHz as shown in Figure 29.

This is described in more detail in <u>Section 4.2 on page 19</u> and in the OL2381 data sheet.

29 of 143

At low frequencies (434 MHz and 315 MHz), bit RF\_LO\_DIV in register LOCON (address: 0x0D) must be set to logic 1. For high frequencies (868 MHz and 915 MHz), bit RF\_LO\_DIV must be set to logic 0.

At 434 MHz/868 MHz/915 MHz operation, only OL2381 chip version X1A can be used and bit VCO Band has to be set to logic 0. At 315 MHz operation, only OL2381 X1B version can be used with the VCO Band set to logic 1.

Figure 30 shows how register LOCON (address: 0x0D) and especially bits RF LO DIV and VCO BAND are configured for 434 MHz.

The PLL charge pump also needs to be set. After RESET command, bit PLL ICP in register EXPERT0 is set to 0x04. Bit PLL\_ICP should be set to 0x02 for proper operation as shown in Figure 19 on page 19.

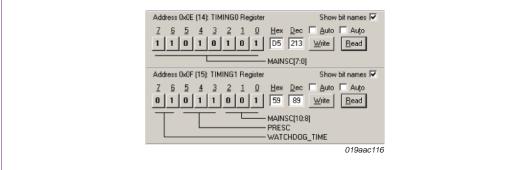

# 5.4 Baud rate configuration

After setting the PLL charge pump, the baud rate must be set next. The baud rate generator creates the nominal, unsynchronized chip clock and is calculated by Equation 5.

chip\_rate =

$$\frac{f_{ref}}{2^{PRESC}} \times \frac{2^{11} + MAINSC}{2^{12}} \times \frac{1}{128}$$

(5)

Where:

f<sub>ref</sub> is the reference frequency, which in this application is: 16 MHz.

PRESC is an exponent in the range 0 to 7.

2<sup>11</sup> + MAINSC is the mantissa in the range 2048 to 4095.

It is possible to determine the values of registers TIMING0 and TIMING1 by using the inverse function as shown in Equation 6, Equation 7 and Equation 8.

$$kchip = \frac{\text{chip}_{ref} \times 4096 \times 128}{f_{ref}} = \frac{2048 + MAINSC}{2^{PRESC}}$$

(6)

$$PRESC = \left\lfloor \log_2 \left( \frac{8191}{2 \times max(25, min(3000, kchip))} \right) \right\rfloor$$

(7)

$$MAINSC = max(0,\min(2047, \lfloor kchip \times 2^{PRESC} - 2047.5 \rfloor))$$

(8)

#### General application note for OL2381

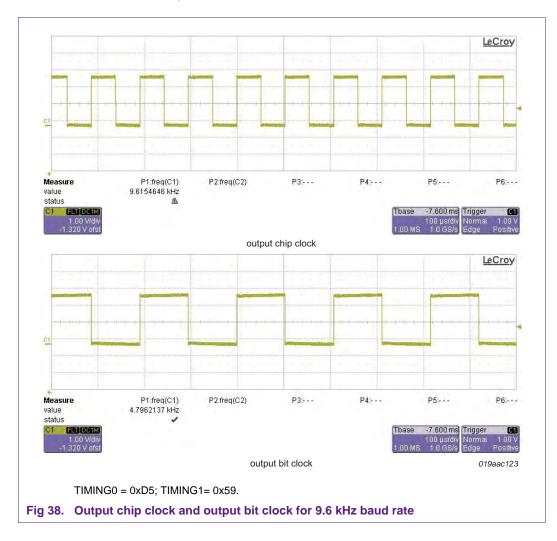

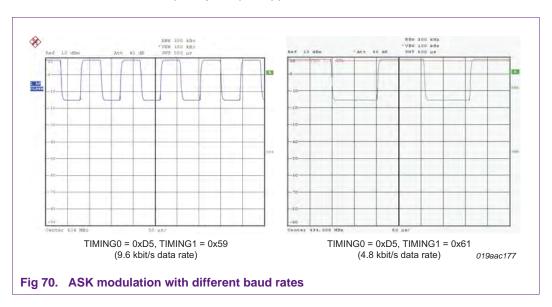

Registers TIMING0 (address: 0x0E) and TIMING1 (address: 0x0F) are set to 0xD5 and 0x59 for a baud rate of 9.6 kbit/s as shown in Figure 31.

#### Fig 31. Configuration of 9.6 kbit/s baud rate

Table 12 shows the settings for different baud rates that can be used with the OL2381.

Table 12. Different baud rate settings

| Baud rate (kbit/s) | TIMING0 | TIMING1 | PRESC | MAINSC |

|--------------------|---------|---------|-------|--------|

| 2.4                | 0xD5    | 0x69    | 5d    | 469d   |

| 4.8                | 0xD5    | 0x61    | 4d    | 469d   |

| 9.6                | 0xD5    | 0x59    | 3d    | 469d   |

| 19.2               | 0xD5    | 0x51    | 2d    | 469d   |

# 5.5 Watchdog timer

The OL2381 features a watchdog timer to recover from situations when activation is not desired.

The watchdog timer is activated when the device leaves Power-down mode and a reference clock is available.

The watchdog is cleared and temporarily stopped under the following circumstances:

- Pin SEN is HIGH

- A terminating wake-up search is executed, i.e. either a pessimistic wake-up search is activated (SIGMON0 register, WUPSMODE bit = 0) or the timer for the wake-up search is activated during an optimistic wake-up search (WUPSMODE = logic 1 and WUPSTO register, WUPSTIMEOUT not equal to logic 0).

- A terminating preamble detection is executed, i.e. the timeout for the preamble must be activated (SIGMON1 register, EN\_PREADET\_TIMEOUT bit = logic 1 and WUPSTIMEOUT not equal to logic 0).

It is not possible to turn off the watchdog completely. Only if pin SEN is set HIGH, the watchdog can be disabled for an arbitrary period.

Bits [7:6] in register TIMING1 are configured as shown in Figure 31. Further details are given in the OL2381 data sheet.

The watchdog timeout can be calculated according to equation Equation 9.

#### **General application note for OL2381**

watchdogtimeout =  $\frac{2^{15 + WATCHDOGTIME}}{CLK_{RFF}}$

Where:  $CLK_{REF} = 16$  MHz.

As an example, if WATCHDOG\_TIME bits are 00, watchdog\_timeout = 2.048 ms.

If WATCHDOG\_TIME bits are 11 watchdog\_timeout = 16.384 ms.

Interrupt flag IF\_WATCHDOG in IFLAG register will be set when a watchdog overflow occurs. This interrupt is maskable.

The Graphical User Interface (GUI) software which NXP provides does not keep the SEN line HIGH but the watchdog timer is used and can be evaluated.

In real applications, the SEN line should be cleared by the microcontroller after any command sent to the OL2381 which will ensure the correct watchdog timer usage. This will automatically turn off OL2381 after a certain period of inactivity. The watchdog timeout should be properly adjusted according to the specific application.

To disable the watchdog in the application, line SEN should be kept HIGH by software.

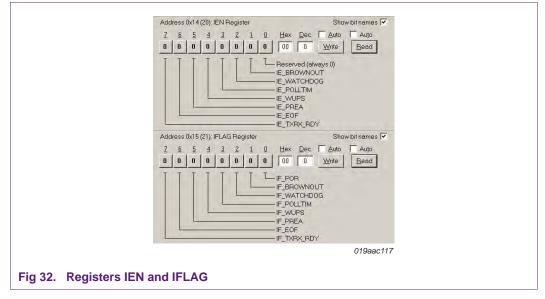

#### 5.6 Interrupts

OL2381 can generate interrupts for some specific events (TX/RX ready, End-Of-Frame, preamble detection, WUPS, polling event, watchdog, reset). More details are available in the OL2381 data sheet.

Two kinds of interrupts can be produced: maskable and non-maskable.

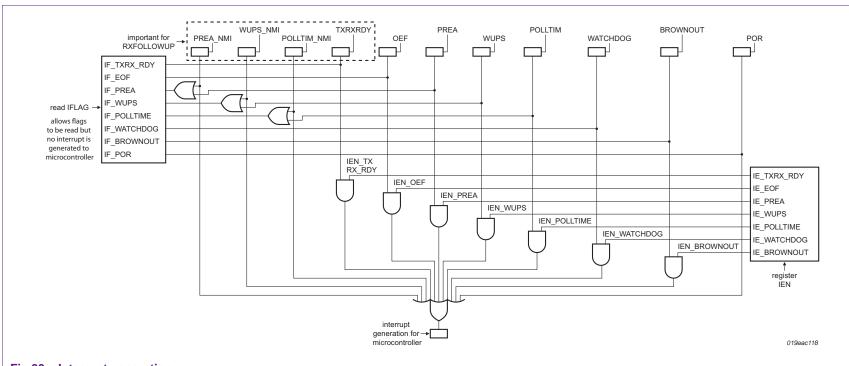

In order to generate an interrupt, the bit corresponding to the event needs to be set in register IEN (address: 0x14). The corresponding bit in register IFLAG is always set in case an event occurs, but an interrupt will not be generated if the corresponding bit in register IEN is not set. There are four events that can generate an interrupt to the microcontroller without setting the bits in register IEN. These are the non-maskable interrupts:

- POR: Power-On Reset

- POLLTIM: POLLing TIMer event

- WUPS: Wake-UP Search event

- PREA: PREAmble detection event

POR is the only event that always generates a non-maskable interrupt. POLLTIM, WUPS, PREA could be maskable, or not, depending on the user's circumstances. Other interrupts (TXRXRDY, WATCHDOG, and BROWNOUT) are only maskable.

When an event occurs, the bit corresponding to the event will be set in register IFLAG (address: 0x15). Register IFLAG is cleared after it is read. Reading register IFLAG also clears the interrupt line.

Registers IEN and IFLAG are shown in Figure 32.

(9)

General application note for OL2381

Figure 33 shows how interrupts are processed in relation to the configuration of registers IFLAG and IEN.

All information provided in this document is subject to legal disclain Rev. 1 — 22 August 2011

AN11039

Application note

Fig 33. Interrupt generation

Special attention should be made when OL2381 is reset. The reset (default) state of register PORTCON0 sets the interrupt line (P11) to the inverted state.

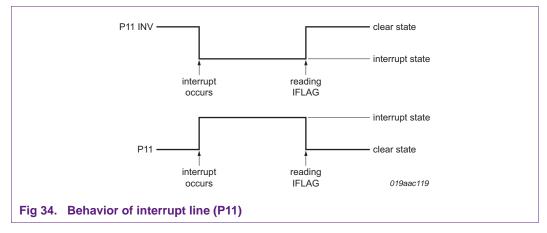

Figure 34 shows the behavior of interrupt line (P11) in relation to its configuration. P11INV corresponds to 00101000 in PORTCON0 and P11 to 00100000.

WUPS, PREA and POLLTIM interrupts can be maskable, or not, depending on the OL2381 configuration.

| Table 13. Interrupt \ | WUPS/PREA |

|-----------------------|-----------|

|-----------------------|-----------|

| Maskable WUPS/PREA interrupts                  | Non-maskable WUPS/PREA interrupts                                         |

|------------------------------------------------|---------------------------------------------------------------------------|

| When WUPS/PREA is finished (successful or not) | when a receive command is initiated by a polling timer                    |

|                                                | AND OL2381 does not go to PD (if unsuccessful)                            |

|                                                | AND if OL2381 goes to DATA mode (if successful) or STOP (if unsuccessful) |

If a maskable interrupt occurs, the corresponding bits (IE\_WUPS/IE\_PREA) need to be set in register IEN to generate an interrupt when maskable WUPS/PREA events occur.

| Maskable POLLTIM interrupt       | Non-maskable POLLTIM interrupt                                           |  |  |

|----------------------------------|--------------------------------------------------------------------------|--|--|

| When the polling timer overflows | in polling modes 0 and 1 (POL_MODE = 00 and 01)                          |  |  |

|                                  | in polling mode 2 (POL_MODE = 10) when<br>TX/RX interrupt is not enabled |  |  |

|                                  | in polling mode 3 (POL_MODE = 11) when TX/RX interrupt is not enabled    |  |  |

|                                  | AND OL2381 executes a CONT or DATA<br>receive command                    |  |  |

|                                  | AND OL2381 uses the old TX/RX flags from<br>the previous command         |  |  |

### 5.7 Clock configuration

OL2381 can provide different clock signals according to the application. Some examples are shown in this section.

### 5.7.1 External clock from register CLOCKCON

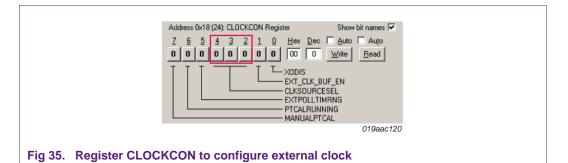

An external clock can be generated for the microcontroller for another application independent of the OL2381. The register CLOCKCON (address: 0x18) shown in <u>Figure 35</u> and in particular, bits CLKSOURCESEL allow generation of an external clock on P12/CLOCK or P11/INV.

All information provided in this document is subject to legal disclaimers.

Table 15 shows the configuration of bits CLKSOURCESEL. The chip clock is configured by registers TIMING0 and TIMING1 (address: 0x0E-0x0F). Further details about the chip rate generation are given in Section 5.4 on page 30.

Table 15. Configuration of bits CLKSOURCESEL

| CLKSOURCESEL | External clock/port pin | Clock frequency<br>measurements |

|--------------|-------------------------|---------------------------------|

| 000          | reference clock         | 16 MHz                          |

| 001          | reference clock / 2     | 8 MHz                           |

| 010          | reference clock / 4     | 4 MHz                           |

| 011          | reference clock / 8     | 2 MHz                           |

| 100          | 4 x chip clock          | 38.4 kHz                        |

| 101          | 2 x chip clock          | 19.2 kHz                        |

| 110          | chip clock              | 9.6 kHz                         |

| 111          | bit clock               | 4.8 kHz                         |

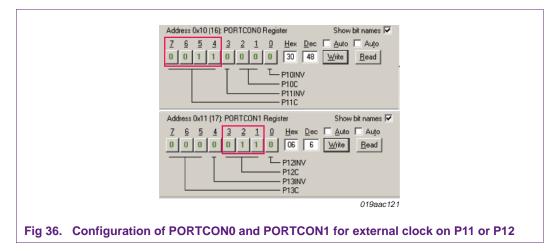

To generate an external clock, P12/CLOCK or P11/INV must be set to 011 or 0011 as shown in Figure 36.

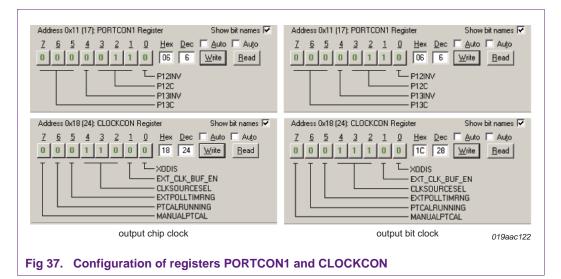

A bit or chip clock signal can be observed with an oscilloscope connected to pin P12 if register PORTCON1 is configured as output clock from clock generation according to the settings of CLKSOURCESEL (Figure 37). This is shown in Figure 38.

### General application note for OL2381

The value of CLKSOURCESEL does not have any influence on the data generation in transmit mode or data reception in receive mode.

All information provided in this document is subject to legal disclaimers.

AN11039

37 of 143

#### 5.7.2 External 1 MHz clock

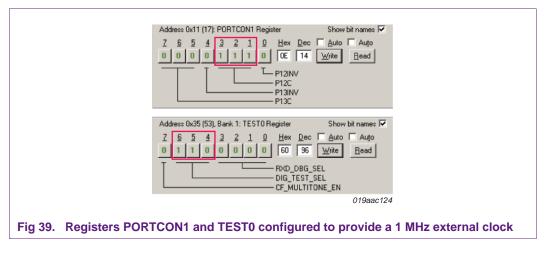

A fixed external clock of 1 MHz can be generated with port P12/CLOCK and the digital test signal as shown in Figure 39.

#### 5.7.3 TX clock

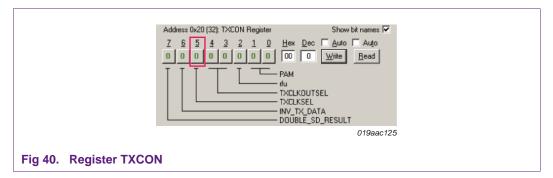

A TX clock can be provided on pin SCLK or P12/CLOCK in order to send data. A bit clock or a chip clock can be generated depending on the application.

Bit TXCLKSEL in register TXCON (address: 0x20) determines if the OL2381 generates the chip clock (bit TXCLKSEL = logic 0) or the bit clock (bit TXCLKSEL = logic 1) as shown in Figure 40.

In normal use situations, the chip clock is set as the TX clock when NRZ encoding is used and the bit clock is set as the TX clock when Manchester encoding is used, as shown in <u>Table 16</u>. Further details of the chip rate calculation are given in <u>Section 5.4 on page 30</u>.

#### Table 16. Transmit clock options

Further information about transmit flag TE is available in <u>Section 6.3 on page 43</u>.

| TXCLKSEL | Transmit flag TE | Transmitter clock | User case                                                           |

|----------|------------------|-------------------|---------------------------------------------------------------------|

| 0        | 0                | chip clock        | transmitting NRZ data, or a chip sequence encoded by the controller |

| 1        | 1                | bit clock         | transmitting Manchester encoded data                                |

To generate the TX clock, a transmit command must be activated (see Figure 50 on page 43).

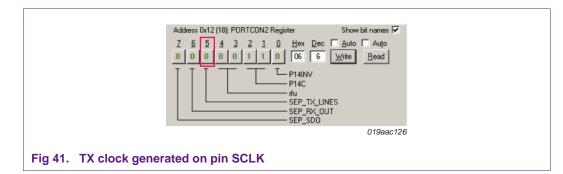

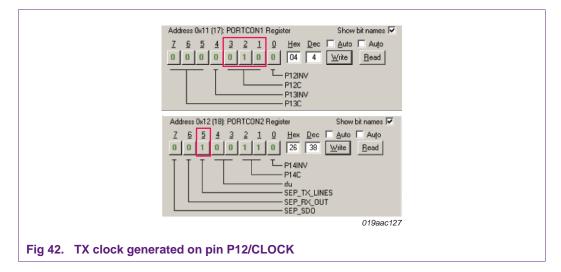

To generate TX clock on pin SCLK or P12/CLOCK, registers PORTCON1 and PORTCON2 must be configured (see Figure 41 and Figure 42).

#### 5.7.4 RX clock

The receiver uses the programmed chip rate as the nominal chip rate of the expected receive signal. The chip rate of the received signal must be within  $\pm 1$  % of the programmed nominal chip rate. Further details are given in the OL2381 data sheet. The chip rate is calculated as shown in Equation 6, Equation 7 and Equation 8 in Section 5.4 on page 30.

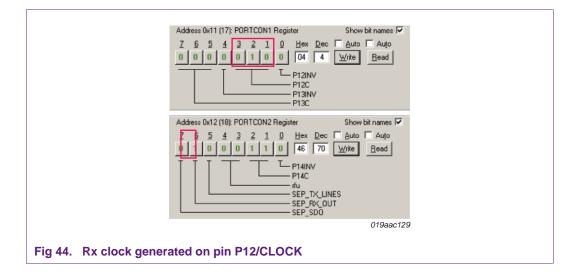

The RX clock can be received on either pin SCLK or P12/CLOCK. Registers PORTCON1 and PORTCON2 must be configured as shown in <u>Figure 43</u> or <u>Figure 44</u> in order to generate the clock on pin SCLK or P12/CLOCK.

The clock is recovered from the received signal timing and informs the microcontroller when it is ready to sample data delivered at P10/DATA or SCLK.

#### 5.7.5 Additional functions

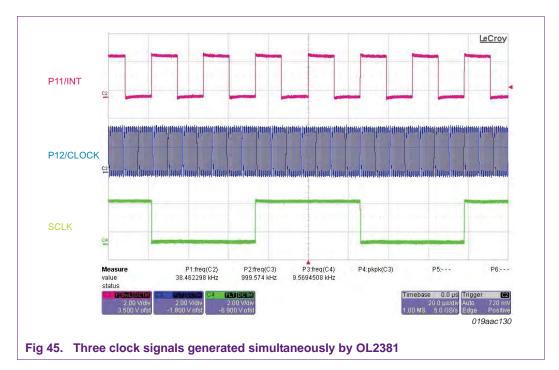

The OL2381 can provide up to three clock signals simultaneously. As an example, the OL2381 could be configured to provide four times the chip rate at pin P11/INT, 1 MHz external clock at pin P12/CLOCK and the transmitter output chip clock at pin SCLK as shown in Figure 45.

OL2381 register configuration for this example is:

Clock at pin P11/INT = 4 × chip rate: PORTCON0 = 0x30; CLOCKCON = 0x10

Clock at pin P12/CLOCK = 1 MHz: PORTCON1 = 0x0E; TEST0 = 0x60

Clock at pin SCLK = transmit output chip clock: PORTCON2 = 0x00; TXCON = 0x00 Chip rate: 9.6 kbit/s: TIMING0 = 0xD5; TIMING1 = 0x59

#### 6. Transmitter operation

#### Introduction 6.1

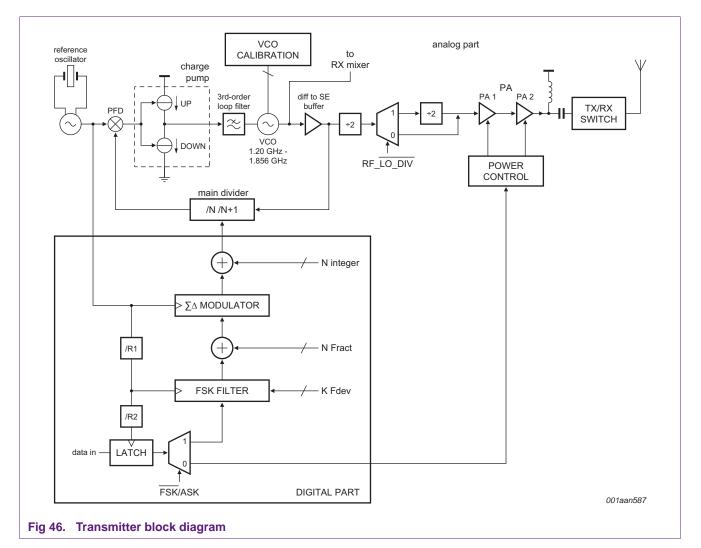

The block diagram of the OL2381 transmitter is shown in Figure 46.

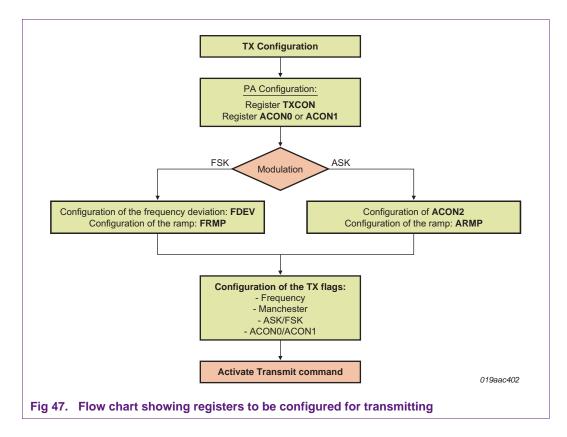

Some OL2381 registers need to be configured for transmitting as shown in Figure 47. The configured registers will change depending on the selected modulation. Some general registers must be configured for both ASK and FSK modulation as shown in Figure 28 on page 28.

#### General application note for OL2381

# 6.2 Power configuration

The power amplifier (PA) supply voltage is configurable to 3 different voltage settings. It is highly advised to use only mode PAM0 for all applications. Configuring OL2381 in PAM0 mode corresponds to a PA supply of 1.5 V and an output power range of -17 dBm to +10 dBm. A more detailed description of the PA settings and matching calculation can be found in Section 6.6.2 on page 62 and in Table 22 on page 65. Figure 40 on page 38 shows register TXCON configured for PAM0.

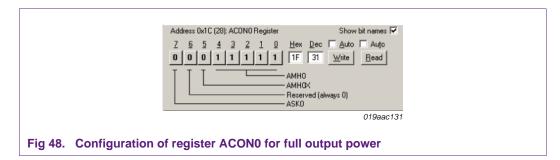

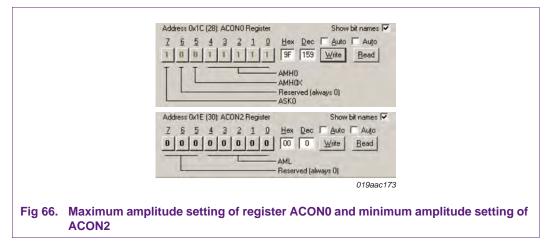

Register ACON0 (address: 0x1C) is set to 0x1F for full power operation as shown in Figure 48.

### 6.3 Transmit mode activation

Transmit mode is initiated by setting control bits DEV\_MODE in register PWRMODE to 11b; see Figure 18 on page 18. In this mode, the state machine switches on all necessary regulators for transmitting and waits for the transmit command to activate the PA output stage.

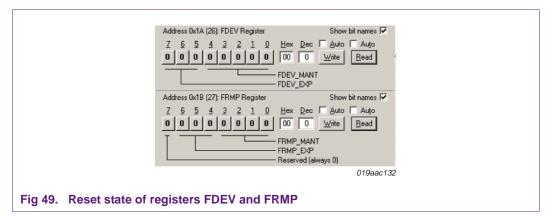

It is recommended to clear all bits of registers FDEV (address: 0x1A) and FRMP (address: 0x1B) as shown in Figure 49 before entering transmit mode.

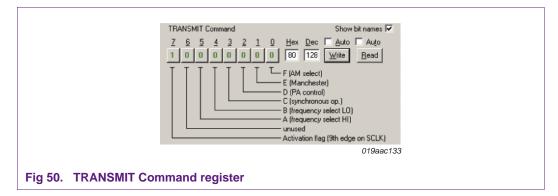

The transmit command must be sent to enable transmit mode. The OL2381 is activated in transmit mode when the register activation flag bit 7 is set, as shown in Figure 50.

The register bits are explained below:

Bits A, B: transmitter frequency selection bits,

Bit C: data and power amplifier synchronization bit,

- Bit D: power amplifier control bit,

- Bit E: Manchester generation bit,

- Bit F: amplitude selection bit.

| Table 17. | Frequency band selection (bits A, B) |                         |  |  |

|-----------|--------------------------------------|-------------------------|--|--|

| Bit A     | Bit B                                | Selected frequency band |  |  |

| 0         | 0                                    | FC0L, FC0M, FC0H        |  |  |

| 0         | 1                                    | FC1L, FC1M, FC1H        |  |  |

| 1         | 0                                    | FC2L, FC2M, FC2H        |  |  |

| 1         | 1                                    | FC3L, FC3M, FC3H        |  |  |

| Table 18. | Power amplifier | mplifier control and synchronization (bits C, D)                                                                                                            |  |  |

|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit C     | Bit D           | Effect                                                                                                                                                      |  |  |

| Х         | 0               | power amplifier stays on after falling edge of SEN                                                                                                          |  |  |

| 0         | 1               | transmitted data is synchronized with the baud rate clock $(CLK_{TX})^{\underline{[1]}}$                                                                    |  |  |

| 1         | 1               | power amplifier is turned off synchronously with the baud rate clock ( $CLK_{TX}$ ) after the falling edge of SEN (PA off-ramping supported) <sup>[1]</sup> |  |  |

[1] Bit C must be specified appropriately even if bit E = 1.

#### Table 19. Power amplifier control and synchronization (bits C, E)

| Bit C | Bit E | Effect                                                                                                                                  |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | transmitted data is unsynchronized (only synchronizes to CLKREF)                                                                        |

| 1     | 0     | transmitted data is synchronized with the baud rate clock ( $CLK_TX$ )                                                                  |

| Х     | 1     | transmitted data is synchronized and XORed with baud rate clock (CLK <sub>TX</sub> ) which applies Manchester generation <sup>[1]</sup> |

[1] If bit E = 1, the value of bit C is ignored and data is always synchronized with the baud rate clock. However, bit C has an effect if bit D = 1. Therefore, bit C must be set correctly even if bit E = 1.

#### Table 20. Amplitude selection (bit F)

| Bit F | Effect                                                                          |

|-------|---------------------------------------------------------------------------------|

| 0     | modulation and amplitude/power settings are applied according to register ACON0 |

| 1     | modulation and amplitude/power settings are applied according to register ACON1 |

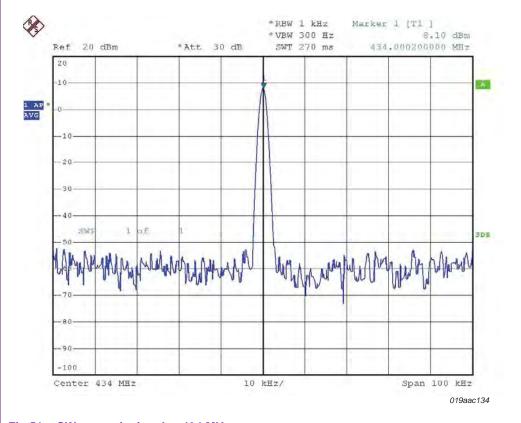

After setting all previously explained registers and sending a transmit command, a CW signal (no modulation) at 434 MHz can be observed on the spectrum analyzer as shown in Figure 51.

#### General application note for OL2381

#### Fig 51. CW transmit signal at 434 MHz

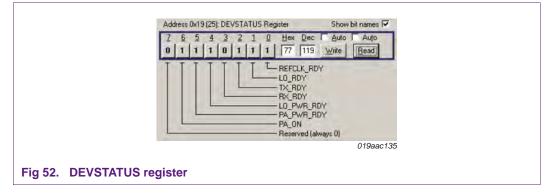

Register DEVSTATUS (address: 0x19) shows the active OL2381 blocks.

The different bits are explained in more detail in the OL2381 data sheet. Bits REFCLK\_RDY, LO\_RDY, TX\_RDY, LO\_PWR\_RDY, PA\_PWR\_RDY, and PA\_ON are set to logic 1 if TX mode is successfully activated, as shown in Figure 52.

# 6.4 FSK modulation

Configuration of additional registers is needed for FSK modulated transmission. Some examples using different data rates and frequency deviations are presented in this document.

#### 6.4.1 Frequency deviation

FSK and GFSK-type modulation are accomplished by adding a time varying sequence to the center frequency control value. It causes the total frequency control value to also vary with time. Since this variation is slow enough to pass the transfer function of the PLL, the resulting RF signal is modulated in frequency. More information are given in the OL2381 data sheet.

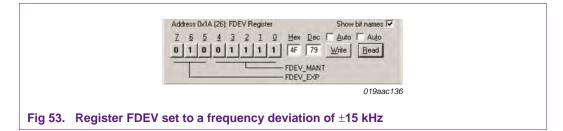

The frequency deviation D of the FSK signal is set in register FDEV. It is computed using Equation 10.

$$D = \left[ 2^{\text{FDEV}\_\text{EXP}} \times \text{FDEV}\_\text{MANT} \times \frac{l}{2} \times \frac{l + \text{RF}\_\text{LO}\_\text{DIV}}{l + \text{DOUBLE}\_\text{SD}\_\text{RESULT}} \right]$$

(10)

Bits RF\_LO\_DIV and DOUBLE\_SD\_RESULT have been included in this expression to compensate for their influence on the frequency resolution. As the selected frequency is 434 MHz, bit RF\_LO\_DIV = logic 1, bit DOUBLE\_SD\_RESULT is logic 0 by default.

The frequency deviation in FSK mode is calculated using Equation 11.

$$f_{dev} = \frac{2^{\text{FDEV}\_\text{EXP}} \times \text{FDEV}\_\text{MANT}}{65536} \times f_{ref}$$

(11)

Where f<sub>ref</sub> is the reference frequency set here to 16 MHz.

The value of register FDEV (address: 0x1A) can be determined by using the inverse function as shown in Equation 12 and Equation 13.

$$FDEV\_EXP = \min\{7, \max\left\{ \left\lfloor \frac{1 + DOUBLE\_SD\_RESULT}{1 + RF\_LO\_DIV} \right\rfloor, \left\lfloor \log_2\left\{ \frac{FDEV}{15.75} \right\} \right\} \right\}$$

(12)

$$FDEV_MANT = min\left\{31, \left\lfloor 0.5 + \frac{FDEV}{2^{FDEV_EXP}}\right\rfloor\right\}$$

(13)

Where FDEV =  $f_{dev} / f_{ref} \times 65536$ .

According to Equation 11, Equation 12 and Equation 13, for a frequency deviation of  $\pm 15$  kHz, register FDEV is set to 0x4F (FDEV\_EXP = 0x02 and FDEV\_MANT = 0x0F) as shown in Figure 53.

Setting the frequency deviation shifts the signal frequency.

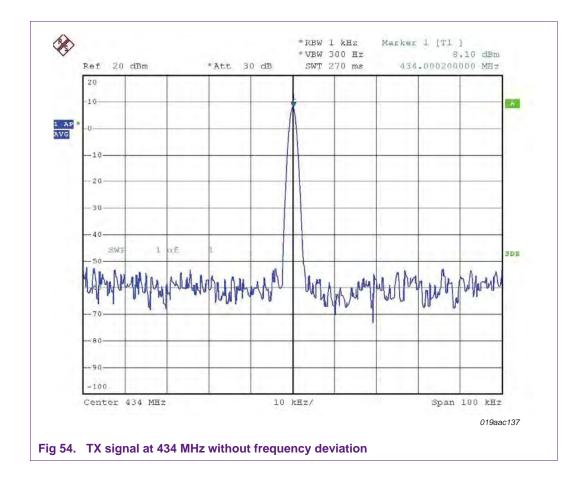

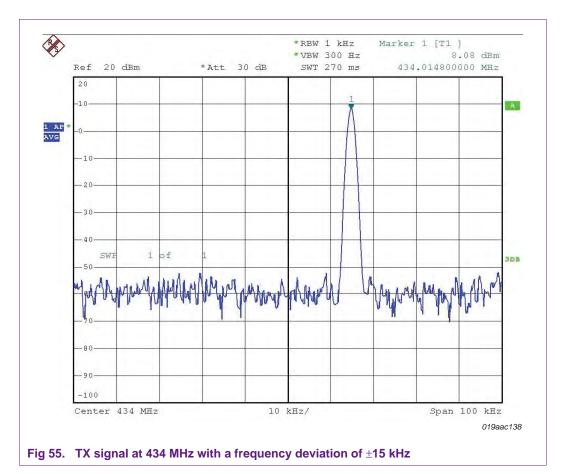

<u>Figure 54</u> and <u>Figure 55</u> show the TX signal at 434 MHz without frequency deviation and with a frequency deviation of  $\pm$ 15 kHz.

### General application note for OL2381

#### General application note for OL2381

# 6.4.2 Frequency modulation

The RF carrier signal must be modulated in order to transmit the data.

The OL2381 graphical user interface (GUI) and the on-chip Manchester encoder can be used as a simple code generator to demonstrate frequency modulated data. It is implemented by keeping the data input constant while the Manchester encoder is active. This produces a square-wave shaped modulated signal corresponding to a sequence of alternating zeros and ones from a data representation point of view.

Transmit command bit E (see Figure 50 on page 43) should be set to logic 1 in this case regardless of the chosen type of modulation. The data will be transmitted Manchester encoded.

If the data rate is 9.6 kbit/s, registers TIMING0 and TIMING1 must be configured according to Figure 31 on page 31.

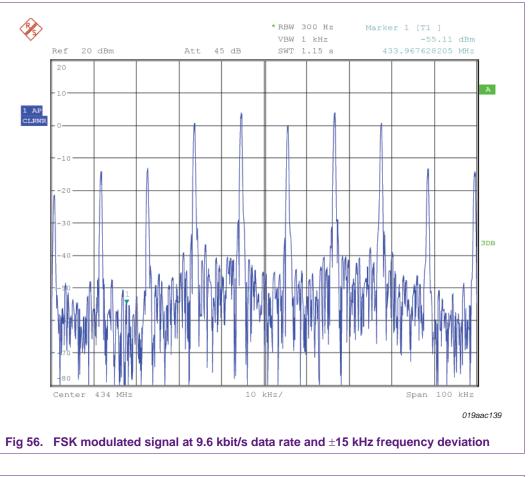

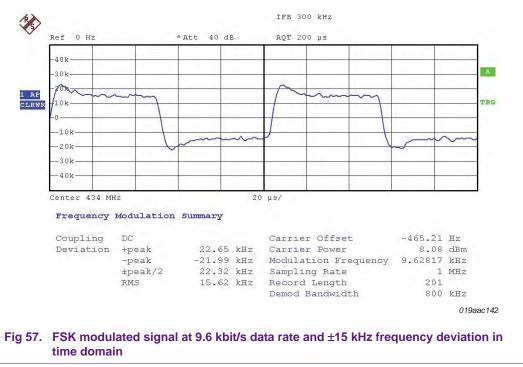

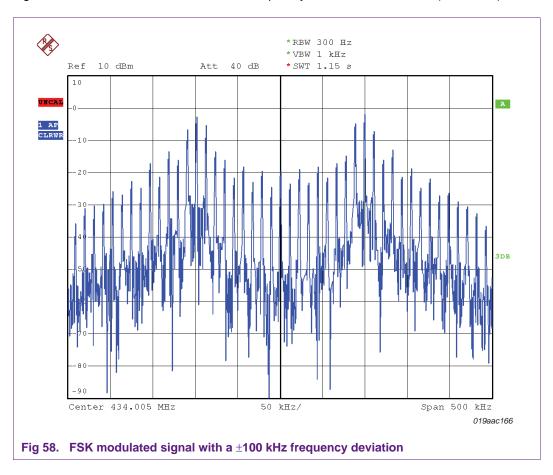

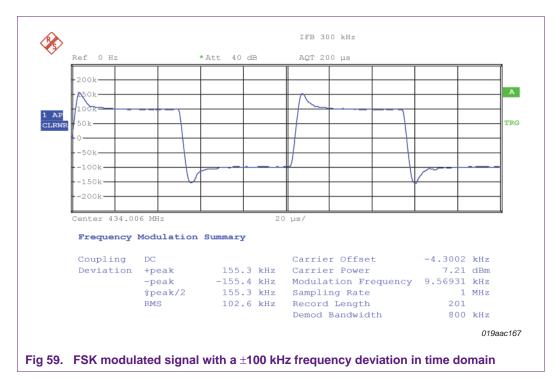

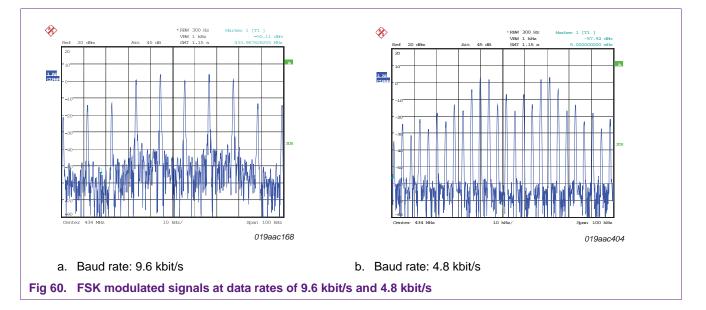

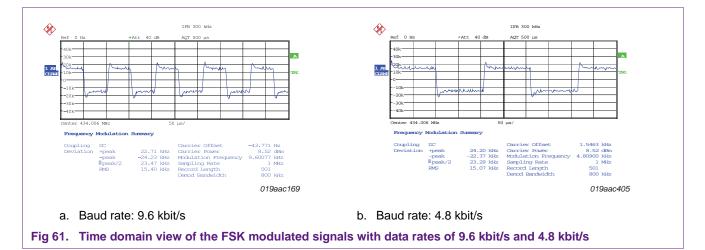

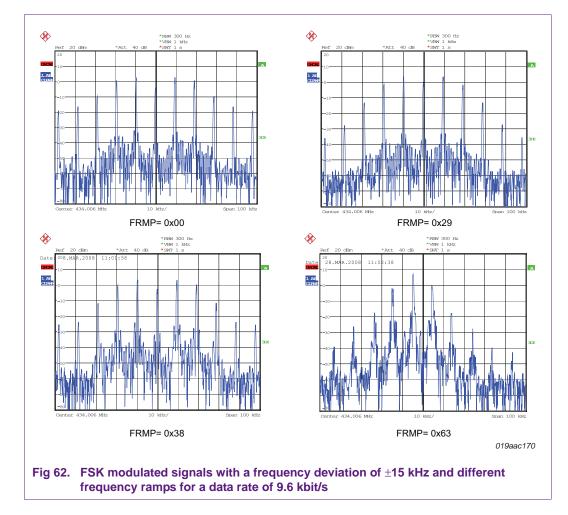

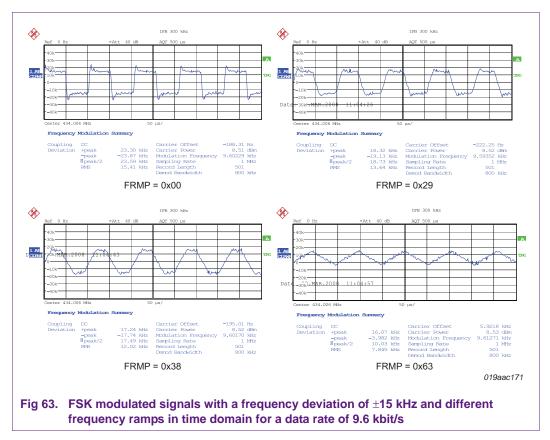

<u>Figure 56</u> and <u>Figure 57</u> show an FSK modulated signal with a data rate of 9.6 kbit/s and a frequency deviation of  $\pm$ 15 kHz in frequency and time domain.

### General application note for OL2381

All information provided in this document is subject to legal disclaimers.

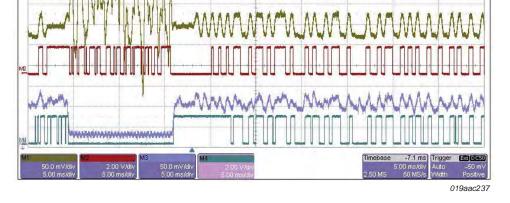

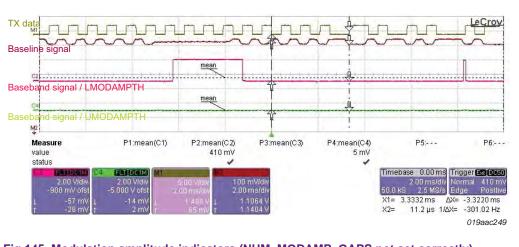

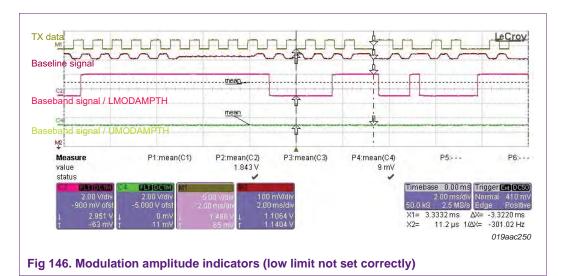

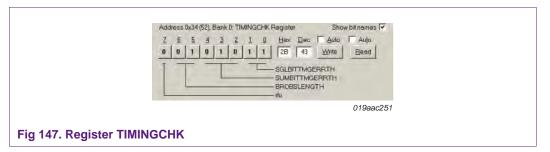

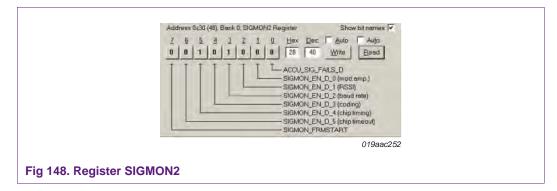

### 6.4.3 Influence of frequency deviation and modulation